Zarówno SoC (System on Chip), jak i SiP (System in Package) stanowią ważne kamienie milowe w rozwoju nowoczesnych układów scalonych, umożliwiające miniaturyzację, wydajność i integrację systemów elektronicznych.

1. Definicje i podstawowe koncepcje SoC i SiP

SoC (System on Chip) – integracja całego systemu w jednym układzie scalonym

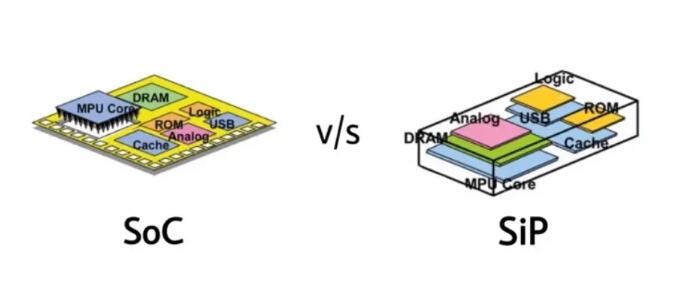

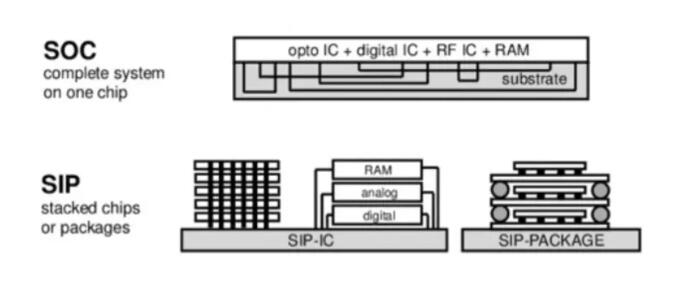

SoC przypomina wieżowiec, w którym wszystkie moduły funkcjonalne są projektowane i integrowane w jednym układzie scalonym. Ideą SoC jest integracja wszystkich kluczowych komponentów systemu elektronicznego, w tym procesora (CPU), pamięci, modułów komunikacyjnych, układów analogowych, interfejsów czujników i różnych innych modułów funkcjonalnych, na jednym układzie scalonym. Zaletami SoC są wysoki stopień integracji i niewielkie rozmiary, co zapewnia znaczące korzyści w zakresie wydajności, poboru mocy i wymiarów, czyniąc go szczególnie odpowiednim dla wysokowydajnych produktów o niskim zużyciu energii. Procesory w smartfonach Apple są przykładami układów SoC.

Dla przykładu, SoC jest jak „superbudynek” w mieście, w którym wszystkie funkcje są zaprojektowane w obrębie jednego układu, a różne moduły funkcjonalne są jak poszczególne piętra: niektóre to biura (procesory), inne to obszary rozrywki (pamięć), a jeszcze inne to sieci komunikacyjne (interfejsy komunikacyjne), wszystkie skoncentrowane w tym samym budynku (chip). Dzięki temu cały system działa na jednym chipie krzemowym, osiągając wyższą wydajność i efektywność.

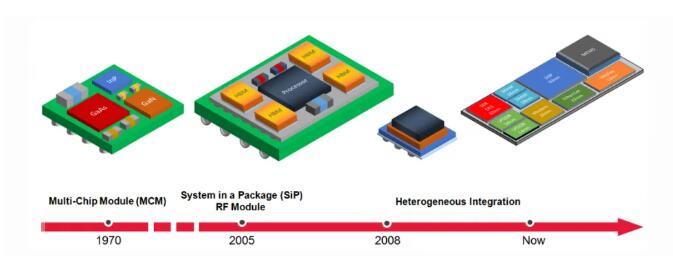

SiP (System in Package) – łączenie różnych układów scalonych

Podejście technologii SiP jest inne. Przypomina ona raczej pakowanie wielu układów scalonych o różnych funkcjach w tej samej obudowie. Koncentruje się ona na łączeniu wielu funkcjonalnych układów scalonych za pomocą technologii pakowania, a nie na ich integracji w jednym układzie, jak w przypadku SoC. SiP umożliwia pakowanie wielu układów scalonych (procesorów, pamięci, układów RF itp.) obok siebie lub w jednym module, tworząc rozwiązanie systemowe.

Koncepcję SiP można porównać do składania skrzynki narzędziowej. Skrzynka może zawierać różne narzędzia, takie jak wkrętaki, młotki i wiertarki. Chociaż są to niezależne narzędzia, wszystkie są zunifikowane w jednym pudełku, co zapewnia wygodę użytkowania. Zaletą tego podejścia jest to, że każde narzędzie można opracować i wyprodukować oddzielnie, a następnie „zmontować” je w pakiet systemowy w razie potrzeby, co zapewnia elastyczność i szybkość.

2. Charakterystyka techniczna i różnice między SoC i SiP

Różnice w metodach całkowania:

SoC: Różne moduły funkcjonalne (takie jak procesor, pamięć, wejścia/wyjścia itp.) są projektowane bezpośrednio na tym samym układzie scalonym. Wszystkie moduły korzystają z tego samego procesu i logiki projektowej, tworząc zintegrowany system.

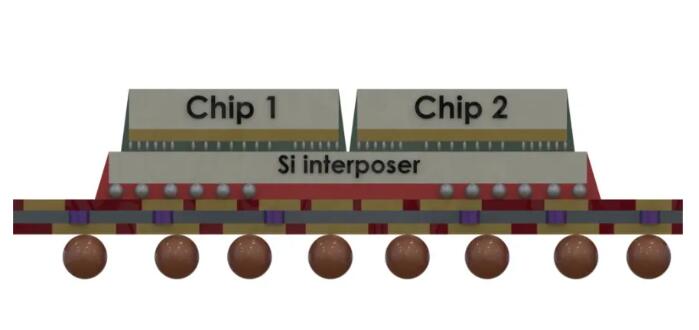

SiP: Różne funkcjonalne układy scalone mogą być wytwarzane przy użyciu różnych procesów, a następnie łączone w pojedynczym module obudowy przy użyciu technologii pakowania 3D w celu utworzenia fizycznego systemu.

Złożoność i elastyczność projektowania:

SoC: Ponieważ wszystkie moduły są zintegrowane na jednym chipie, złożoność projektu jest bardzo wysoka, szczególnie w przypadku wspólnego projektowania różnych modułów, takich jak moduły cyfrowe, analogowe, RF i pamięci. Wymaga to od inżynierów dogłębnych umiejętności projektowania międzydomenowego. Co więcej, jeśli wystąpi problem projektowy z dowolnym modułem w SoC, cały chip może wymagać przeprojektowania, co stwarza znaczne ryzyko.

SiP: Z kolei SiP oferuje większą elastyczność projektowania. Różne moduły funkcjonalne można projektować i weryfikować oddzielnie przed ich spakowaniem do systemu. W przypadku wystąpienia problemu z modułem, wystarczy wymienić tylko ten moduł, pozostawiając pozostałe elementy bez zmian. Pozwala to również na szybsze tempo rozwoju i niższe ryzyko w porównaniu z SoC.

Zgodność procesów i wyzwania:

SoC: Integracja różnych funkcji, takich jak cyfrowe, analogowe i RF, na jednym chipie wiąże się ze znacznymi wyzwaniami w zakresie kompatybilności procesowej. Różne moduły funkcjonalne wymagają różnych procesów produkcyjnych; na przykład, układy cyfrowe wymagają szybkich i energooszczędnych procesów, podczas gdy układy analogowe mogą wymagać bardziej precyzyjnej kontroli napięcia. Osiągnięcie kompatybilności między tymi różnymi procesami na jednym chipie jest niezwykle trudne.

SiP: Dzięki technologii pakowania, SiP umożliwia integrację układów scalonych wytwarzanych w różnych procesach, rozwiązując problemy z kompatybilnością procesową, z którymi boryka się technologia SoC. SiP umożliwia współpracę wielu heterogenicznych układów scalonych w jednej obudowie, ale wymagania dotyczące precyzji w technologii pakowania są wysokie.

Cykl i koszty prac badawczo-rozwojowych:

SoC: Ponieważ SoC wymaga zaprojektowania i weryfikacji wszystkich modułów od podstaw, cykl projektowania jest dłuższy. Każdy moduł musi przejść rygorystyczne projektowanie, weryfikację i testy, a cały proces rozwoju może trwać kilka lat, co generuje wysokie koszty. Jednak po rozpoczęciu produkcji masowej koszt jednostkowy jest niższy ze względu na wysoki poziom integracji.

SiP: Cykl badawczo-rozwojowy SiP jest krótszy. Ponieważ SiP bezpośrednio wykorzystuje istniejące, zweryfikowane i funkcjonalne układy scalone do obudowy, skraca to czas potrzebny na przeprojektowanie modułu. Pozwala to na szybsze wprowadzanie produktów na rynek i znacząco obniża koszty badań i rozwoju.

Wydajność i rozmiar systemu:

SoC: Ponieważ wszystkie moduły znajdują się na tym samym chipie, opóźnienia komunikacji, straty energii i zakłócenia sygnału są minimalizowane, co daje SoC niezrównaną przewagę pod względem wydajności i poboru mocy. Jego minimalny rozmiar sprawia, że jest on szczególnie odpowiedni do aplikacji o wysokich wymaganiach wydajnościowych i energetycznych, takich jak smartfony i układy przetwarzania obrazu.

SiP: Chociaż poziom integracji SiP nie jest tak wysoki jak w przypadku SoC, nadal pozwala on na kompaktowe pakowanie różnych układów scalonych w wielowarstwową technologię pakowania, co przekłada się na mniejsze rozmiary w porównaniu z tradycyjnymi rozwiązaniami wieloprocesorowymi. Co więcej, ponieważ moduły są fizycznie pakowane, a nie zintegrowane na tym samym chipie krzemowym, wydajność może nie dorównywać wydajności SoC, ale nadal spełnia wymagania większości aplikacji.

3. Scenariusze zastosowań dla SoC i SiP

Scenariusze zastosowań dla SoC:

Układ SoC jest zazwyczaj odpowiedni do zastosowań o wysokich wymaganiach dotyczących rozmiaru, poboru mocy i wydajności. Na przykład:

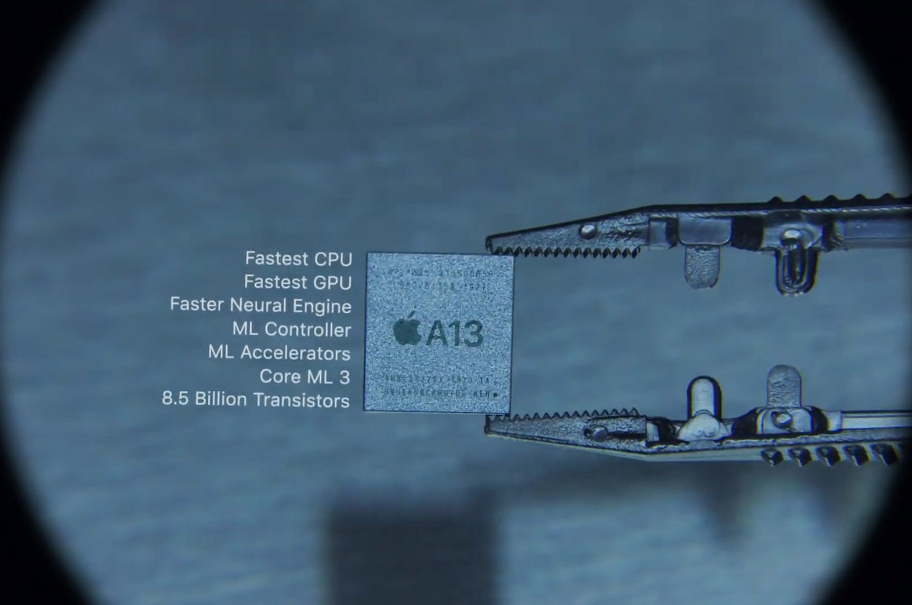

Smartfony: Procesory w smartfonach (takie jak układy Apple z serii A lub Snapdragon firmy Qualcomm) to zwykle wysoce zintegrowane układy SoC, które obejmują procesor główny, procesor graficzny, jednostki przetwarzania sztucznej inteligencji, moduły komunikacyjne itd., wymagające zarówno wysokiej wydajności, jak i niskiego zużycia energii.

Przetwarzanie obrazu: W aparatach cyfrowych i dronach jednostki przetwarzania obrazu często wymagają mocnych możliwości przetwarzania równoległego i niskich opóźnień, co SoC może skutecznie osiągnąć.

Wysokowydajne systemy wbudowane: SoC jest szczególnie odpowiedni dla małych urządzeń o rygorystycznych wymaganiach dotyczących efektywności energetycznej, takich jak urządzenia IoT i urządzenia noszone.

Scenariusze zastosowań dla SiP:

SiP ma szerszy zakres scenariuszy zastosowań, nadaje się do dziedzin wymagających szybkiego rozwoju i wielofunkcyjnej integracji, takich jak:

Sprzęt komunikacyjny: W przypadku stacji bazowych, routerów itp. technologia SiP umożliwia integrację wielu procesorów sygnałów RF i cyfrowych, przyspieszając cykl rozwoju produktu.

Elektronika użytkowa: W przypadku produktów takich jak smartwatche i zestawy słuchawkowe Bluetooth, których cykle aktualizacji są szybkie, technologia SiP pozwala na szybsze wprowadzanie nowych produktów o nowych funkcjach.

Elektronika samochodowa: Moduły sterujące i systemy radarowe w układach samochodowych mogą wykorzystywać technologię SiP do szybkiej integracji różnych modułów funkcjonalnych.

4. Przyszłe trendy rozwoju SoC i SiP

Trendy w rozwoju SoC:

Układ SoC będzie nadal ewoluował w kierunku większej integracji i integracji heterogenicznej, potencjalnie obejmując większą integrację procesorów AI, modułów komunikacji 5G i innych funkcji, co będzie napędzać dalszą ewolucję inteligentnych urządzeń.

Trendy w rozwoju SiP:

SiP będzie w coraz większym stopniu opierać się na zaawansowanych technologiach pakowania, takich jak pakowanie 2,5D i 3D, aby szczelnie pakować ze sobą układy scalone o różnych procesach i funkcjach, co pozwoli sprostać szybko zmieniającym się wymaganiom rynku.

5. Wnioski

SoC bardziej przypomina budowę wielofunkcyjnego superwieżowca, koncentrując wszystkie moduły funkcjonalne w jednym projekcie, co jest odpowiednie dla aplikacji o ekstremalnie wysokich wymaganiach dotyczących wydajności, rozmiaru i zużycia energii. Z kolei SiP to „pakowanie” różnych układów scalonych w system, koncentrując się bardziej na elastyczności i szybkim rozwoju, co jest szczególnie przydatne w przypadku elektroniki użytkowej wymagającej szybkich aktualizacji. Oba rozwiązania mają swoje mocne strony: SoC kładzie nacisk na optymalną wydajność systemu i optymalizację rozmiaru, podczas gdy SiP kładzie nacisk na elastyczność systemu i optymalizację cyklu rozwoju.

Czas publikacji: 28-10-2024