Zarówno SoC (System on Chip), jak i SiP (System in Package) są ważnymi kamieniami milowymi w rozwoju nowoczesnych układów scalonych, umożliwiającymi miniaturyzację, wydajność i integrację systemów elektronicznych.

1. Definicje i podstawowe koncepcje SoC i SiP

SoC (System on Chip) – integracja całego systemu w jednym układzie scalonym

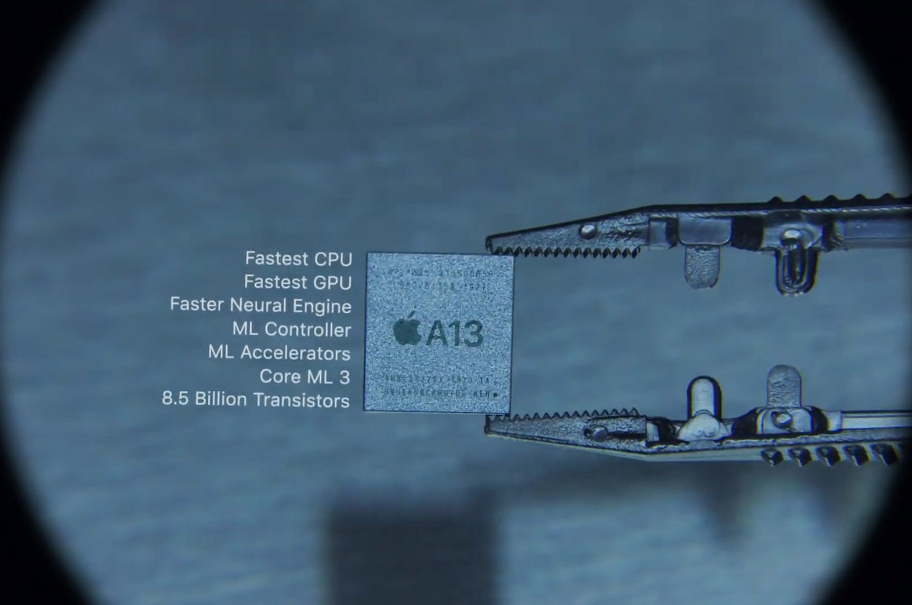

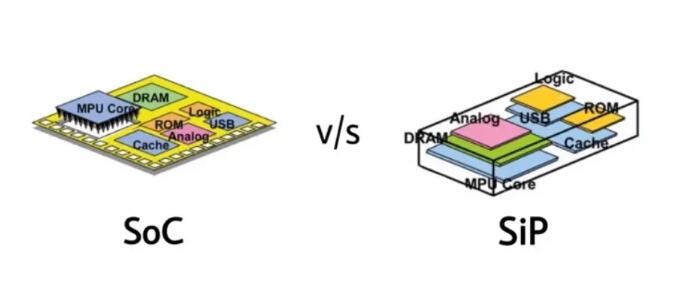

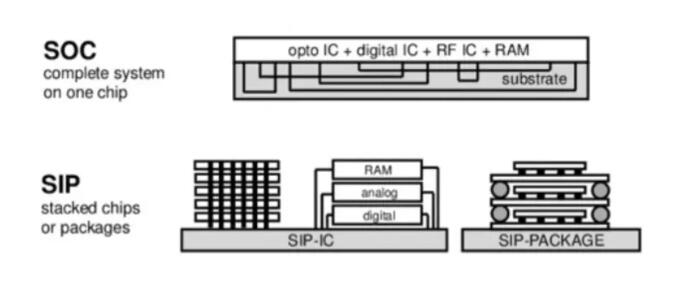

SoC jest jak wieżowiec, w którym wszystkie moduły funkcjonalne są zaprojektowane i zintegrowane w tym samym fizycznym chipie. Podstawowym pomysłem SoC jest zintegrowanie wszystkich podstawowych komponentów systemu elektronicznego, w tym procesora (CPU), pamięci, modułów komunikacyjnych, obwodów analogowych, interfejsów czujników i różnych innych modułów funkcjonalnych, na jednym chipie. Zalety SoC leżą w jego wysokim poziomie integracji i niewielkich rozmiarach, co zapewnia znaczące korzyści w zakresie wydajności, zużycia energii i wymiarów, dzięki czemu jest on szczególnie odpowiedni dla produktów o wysokiej wydajności i wrażliwości na energię. Procesory w smartfonach Apple są przykładami chipów SoC.

Dla przykładu, SoC jest jak „super budynek” w mieście, w którym wszystkie funkcje są zaprojektowane wewnątrz, a różne moduły funkcjonalne są jak różne piętra: niektóre to obszary biurowe (procesory), niektóre to obszary rozrywkowe (pamięć), a niektóre to sieci komunikacyjne (interfejsy komunikacyjne), wszystkie skoncentrowane w tym samym budynku (chip). Dzięki temu cały system może działać na jednym chipie krzemowym, osiągając wyższą wydajność i efektywność.

SiP (System in Package) – łączenie różnych układów scalonych

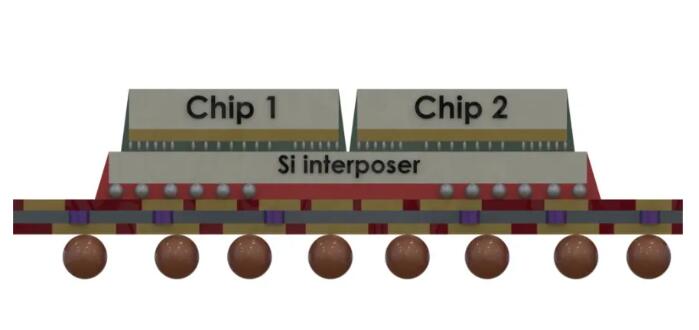

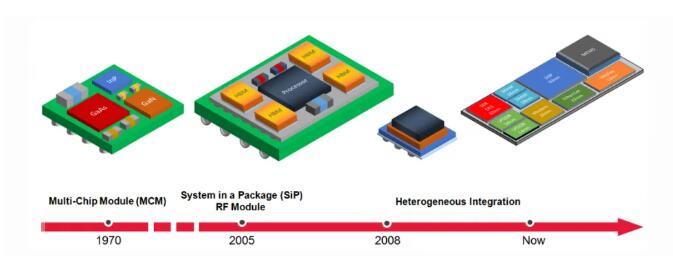

Podejście technologii SiP jest inne. Bardziej przypomina pakowanie wielu układów scalonych o różnych funkcjach w tym samym fizycznym opakowaniu. Skupia się na łączeniu wielu funkcjonalnych układów scalonych za pomocą technologii pakowania, a nie na integrowaniu ich w pojedynczy układ, jak SoC. SiP umożliwia pakowanie wielu układów scalonych (procesorów, pamięci, układów RF itp.) obok siebie lub układanie ich w tym samym module, tworząc rozwiązanie na poziomie systemu.

Koncepcję SiP można porównać do składania skrzynki narzędziowej. Skrzynka narzędziowa może zawierać różne narzędzia, takie jak śrubokręty, młotki i wiertarki. Chociaż są to niezależne narzędzia, wszystkie są zunifikowane w jednym pudełku, co ułatwia użytkowanie. Zaletą tego podejścia jest to, że każde narzędzie można opracować i wyprodukować osobno, a następnie można je „zmontować” w pakiet systemowy w razie potrzeby, zapewniając elastyczność i szybkość.

2. Charakterystyka techniczna i różnice między SoC i SiP

Różnice w metodach integracji:

SoC: Różne moduły funkcjonalne (takie jak CPU, pamięć, I/O itp.) są projektowane bezpośrednio na tym samym krzemowym chipie. Wszystkie moduły mają ten sam podstawowy proces i logikę projektową, tworząc zintegrowany system.

SiP: Różne układy scalone o różnych funkcjach mogą być produkowane przy użyciu różnych procesów, a następnie łączone w pojedynczym module obudowy przy użyciu technologii pakowania 3D w celu utworzenia fizycznego systemu.

Złożoność i elastyczność projektu:

SoC: Ponieważ wszystkie moduły są zintegrowane na jednym chipie, złożoność projektu jest bardzo wysoka, szczególnie w przypadku wspólnego projektowania różnych modułów, takich jak cyfrowe, analogowe, RF i pamięci. Wymaga to od inżynierów głębokich możliwości projektowania międzydomenowego. Ponadto, jeśli istnieje problem projektowy z jakimkolwiek modułem w SoC, cały chip może wymagać przeprojektowania, co stwarza znaczne ryzyko.

SiP: Z kolei SiP oferuje większą elastyczność projektowania. Różne moduły funkcjonalne można projektować i weryfikować oddzielnie przed umieszczeniem ich w systemie. Jeśli wystąpi problem z modułem, należy wymienić tylko ten moduł, pozostawiając inne części bez zmian. Pozwala to również na szybsze prędkości rozwoju i niższe ryzyko w porównaniu z SoC.

Zgodność procesów i wyzwania:

SoC: Integracja różnych funkcji, takich jak cyfrowe, analogowe i RF na jednym chipie, wiąże się ze znacznymi wyzwaniami w zakresie zgodności procesów. Różne moduły funkcjonalne wymagają różnych procesów produkcyjnych; na przykład obwody cyfrowe wymagają szybkich procesów o niskim poborze mocy, podczas gdy obwody analogowe mogą wymagać bardziej precyzyjnej kontroli napięcia. Osiągnięcie zgodności między tymi różnymi procesami na tym samym chipie jest niezwykle trudne.

SiP: Dzięki technologii pakowania SiP może integrować chipy produkowane przy użyciu różnych procesów, rozwiązując problemy ze zgodnością procesów, z którymi boryka się technologia SoC. SiP umożliwia współpracę wielu heterogenicznych chipów w tym samym pakiecie, ale wymagania dotyczące precyzji dla technologii pakowania są wysokie.

Cykl i koszty prac badawczo-rozwojowych:

SoC: Ponieważ SoC wymaga projektowania i weryfikacji wszystkich modułów od podstaw, cykl projektowania jest dłuższy. Każdy moduł musi przejść rygorystyczny projekt, weryfikację i testowanie, a cały proces rozwoju może trwać kilka lat, co wiąże się z wysokimi kosztami. Jednak po wprowadzeniu do masowej produkcji koszt jednostkowy jest niższy ze względu na wysoką integrację.

SiP: Cykl badań i rozwoju jest krótszy w przypadku SiP. Ponieważ SiP bezpośrednio wykorzystuje istniejące, zweryfikowane funkcjonalne układy scalone do pakowania, skraca czas potrzebny na przeprojektowanie modułu. Pozwala to na szybsze wprowadzanie produktów na rynek i znacznie obniża koszty badań i rozwoju.

Wydajność i rozmiar systemu:

SoC: Ponieważ wszystkie moduły znajdują się na tym samym chipie, opóźnienia komunikacji, straty energii i zakłócenia sygnału są minimalizowane, co daje SoC niezrównaną przewagę w wydajności i zużyciu energii. Jego rozmiar jest minimalny, co czyni go szczególnie odpowiednim do aplikacji o wysokich wymaganiach wydajnościowych i energetycznych, takich jak smartfony i chipy przetwarzania obrazu.

SiP: Chociaż poziom integracji SiP nie jest tak wysoki jak SoC, nadal może kompaktowo pakować różne chipy razem, wykorzystując technologię pakowania wielowarstwowego, co skutkuje mniejszym rozmiarem w porównaniu do tradycyjnych rozwiązań wielochipowych. Ponadto, ponieważ moduły są fizycznie pakowane, a nie zintegrowane na tym samym krzemowym chipie, podczas gdy wydajność może nie dorównywać wydajności SoC, nadal może spełniać potrzeby większości aplikacji.

3. Scenariusze zastosowań dla SoC i SiP

Scenariusze zastosowań dla SoC:

SoC jest zazwyczaj odpowiedni dla pól o wysokich wymaganiach co do rozmiaru, zużycia energii i wydajności. Na przykład:

Smartfony: Procesory w smartfonach (np. układy Apple z serii A lub Qualcomm Snapdragon) to zazwyczaj wysoce zintegrowane układy SoC, które obejmują procesor główny, procesor graficzny, jednostki przetwarzania AI, moduły komunikacyjne itd., wymagające zarówno wysokiej wydajności, jak i niskiego zużycia energii.

Przetwarzanie obrazu: W aparatach cyfrowych i dronach jednostki przetwarzania obrazu często wymagają mocnych możliwości przetwarzania równoległego i niskich opóźnień, co SoC może skutecznie zapewnić.

Wysokowydajne systemy wbudowane: SoC nadaje się szczególnie do małych urządzeń o rygorystycznych wymaganiach dotyczących efektywności energetycznej, takich jak urządzenia IoT i urządzenia noszone na ciele.

Scenariusze zastosowań dla SiP:

Technologia SiP ma szerszy zakres scenariuszy zastosowań, odpowiednich dla dziedzin wymagających szybkiego rozwoju i wielofunkcyjnej integracji, takich jak:

Sprzęt komunikacyjny: W przypadku stacji bazowych, routerów itp. technologia SiP umożliwia integrację wielu procesorów sygnałów RF i cyfrowych, co przyspiesza cykl rozwoju produktu.

Elektronika użytkowa: W przypadku produktów takich jak smartwatche i zestawy słuchawkowe Bluetooth, które charakteryzują się krótkim cyklem aktualizacji, technologia SiP umożliwia szybsze wprowadzanie nowych produktów z nowymi funkcjami.

Elektronika samochodowa: Moduły sterowania i systemy radarowe w systemach samochodowych mogą wykorzystywać technologię SiP do szybkiej integracji różnych modułów funkcjonalnych.

4. Przyszłe trendy rozwojowe SoC i SiP

Trendy w rozwoju SoC:

Układ SoC będzie nadal ewoluował w kierunku większej integracji i integracji heterogenicznej, co potencjalnie będzie wiązać się z większą integracją procesorów AI, modułów komunikacji 5G i innych funkcji, co będzie napędzać dalszą ewolucję inteligentnych urządzeń.

Trendy w rozwoju SiP:

SiP będzie w coraz większym stopniu opierać się na zaawansowanych technologiach pakowania, takich jak postęp w pakowaniu 2,5D i 3D, aby ściśle pakować ze sobą układy scalone o różnych procesach i funkcjach, spełniając w ten sposób szybko zmieniające się wymagania rynku.

5. Wnioski

SoC jest bardziej jak budowanie wielofunkcyjnego superwieżowca, skupiającego wszystkie moduły funkcjonalne w jednym projekcie, odpowiedniego do zastosowań o ekstremalnie wysokich wymaganiach dotyczących wydajności, rozmiaru i zużycia energii. Z drugiej strony SiP jest jak „pakowanie” różnych układów scalonych w system, skupiając się bardziej na elastyczności i szybkim rozwoju, szczególnie odpowiednim dla elektroniki użytkowej, która wymaga szybkich aktualizacji. Oba mają swoje mocne strony: SoC kładzie nacisk na optymalną wydajność systemu i optymalizację rozmiaru, podczas gdy SiP podkreśla elastyczność systemu i optymalizację cyklu rozwoju.

Czas publikacji: 28-paź-2024